International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

# Vol. 5, Issue 7, July 2016

# Design and Simulation of Error Correction Codes

Chaitra Vardhini H<sup>1</sup>, Prof. Madhu Patil<sup>2</sup>

M. Tech Scholar, Department of ECE, NMIT, Bangalore, India<sup>1</sup>

Associate Professor, Department of ECE, NMIT, Bangalore, India<sup>2</sup>

Abstract: Natural interference like EMI, noise, crosstalk can happen over the communication channel like memory, which causes the original data to be different from the stored data. In order to find these errors a few techniques to recognize and correct the error is required. This work is an overview of different Error Correction techniques. These techniques guarantee to find and possibly correct the errors brought about by the stuck-at faults in the memory. The work is mainly focused on Hamming codes, Convolution codes, CRC and Turbo codes.

Keywords: Hamming codes, Convolution codes, CRC - Cyclic Redundancy Check and Turbo codes.

#### **I. INTRODUCTION**

Environmental interference and physical defects like errors happen. Hamming Codes (n, k) adds n-k no of noise, EMI and crosstalk in the communication channel check bits to every k -bits of message data. can cause random errors during data transmission. The method of detecting and correcting these random errors to ensure information is transferred intact from its source to its destination is called Error coding. Error coding is used for fault tolerant computing in computer memory, satellite communication, space communication, magnetic data storage and optical storage media network communications, cellular telephonic networks, and digital data communication. Error coding encodes the information bits into longer bits called code words for transmitting the data. These code words can be decoded at reception in order to get the original information bits. Redundancy is because of the extra bits that is present in the code word that will allow the reception to use the decoding process to find if the communication medium introduced errors and in some cases correct them so that the data need not be retransmitted.

#### **II. METHODOLOGY**

Initially, the input data bits are given to the encoder, where encoder converts input data bits into code words. Then this Convolutional codes are designed using two parameters: encoded sequence is stored on to the memory. Memory is 1 introduced with a stuck-at-fault (error) which might be either stuck-at-0 or stuck-at-1. The data in the memory is read and given as the input to the decoder. Decoder detects the fault and possibly the position of the fault present in the memory.

## **III. HAMMING CODES**

Hamming codes is called after its designer; Richard Hamming from Bell Labs is a Linear Error Correction Codes. Hamming codes can detect two bit errors and correct single bit error. If the Hamming distance between the sent data and the received data bit is less than or equal to one then reliable communication is possible. It is not reasonable for transmission circumstance where burst

| DATA INPUT  | 11000100                            | 10011010                            |

|-------------|-------------------------------------|-------------------------------------|

| DATA WITH   | P1 P2 1 P4 100 P8 0100              | P1 P2 1 P4 001 P8 1010              |

| PARITY BITS |                                     |                                     |

|             | P1 XOR of bits (3, 5, 7, 9, 11)     | P1 XOR of bits (3, 5, 7, 9, 11)     |

| CALCULATION | P2 XOR of bits (3, 6, 7, 10, 11)    | P2 XOR of bits (3, 6, 7, 10, 11)    |

| OF PARITY   | P4 XOR of bits (5, 6, 7, 12)        | P4 XOR of bits (5, 6, 7, 12)        |

| BITS        | P8 XOR of bits (9, 10, 11, 12)      | P8 XOR of bits (9, 10, 11, 12)      |

| SETPARITY   | 1+1+0+0+0=0 Even Parity P1=0        | 1+0+1+1+1=0 Even Parity P1=0        |

| BITS        | 1+0+0+1+0=0 Even Parity P2=0        | 1+0+1+0+1=1 Odd Parity P2=1         |

| EVEN = 0    | 1+0+0+0=1 Odd Parity P3=1           | 0+0+1+0=1 Odd Parity P3=1           |

| ODD = 1     | 0+1+0+0=1 Odd Parity P4=1           | 1+0+1+0=0 Even Parity P4=1          |

| CODEWORD    | 001110010100                        | 011100101010                        |

| ERROR       |                                     |                                     |

| CODEWORD    | <u>1011100</u> 10100                | 01 <u>11001</u> 0 <u>1110</u>       |

| STORED ON   |                                     |                                     |

| MEMORY      |                                     |                                     |

| EVALUATE    | C1 XOR of bits (1, 3, 5, 7, 9, 11)  | C1 XOR of bits (1, 3, 5, 7, 9, 11)  |

| CHECK BITS  | C2 XOR of bits (2, 3, 6, 7, 10, 11) | C2 XOR of bits (2, 3, 6, 7, 10, 11) |

|             | C4 XOR of bits (4, 5, 6, 7, 12)     | C4 XOR of bits (4, 5, 6, 7, 12)     |

|             | C8 XOR of bits (8, 9, 10, 11, 12)   | C8 XOR of bits (8, 9, 10, 11, 12)   |

| CHECK BITS  | 1+1+1+0+0+0=1 Odd Parity            | 0+1+0+1+1+1=0 Even Parity           |

| PARITY      | 0+1+0+0+1+0=0 Even Parity           | 1+1+0+1+1+1=1 Odd Parity            |

|             | 1+1+0+0+0=0 Even Parity             | 1+0+0+1+0=0 Even Parity             |

|             | 1+0+1+0+0=0 Even Parity             | 0+1+1+1+0=1 Odd Parity              |

| ERROR BIT   | C8C4C2C1=0001                       | C8C4C2C1 = 1010                     |

| POSITION    |                                     |                                     |

Figure 1: (12, 8) Hamming Codes

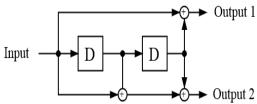

## **IV. CONVOLUTIONAL CODES**

- The code rate

- 2 The constraint length

Code rate -(k/n) is defined as the ratio of the number of bits input to the encoder to the number of bits output by the encoder.

Constraint length (k) denotes the length of convolutional encoder, i.e. how many k-bit stages are available to input the combinatorial logic that produces the output code words

'm' indicates the number of shift registers in the encoder design. It is simply the memory length of the encoder.

Convolutional codes are used in real time communication systems for error correction. The code words depend on the present 'k' message bits and some past input bits. The

# **IJARCCE**

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

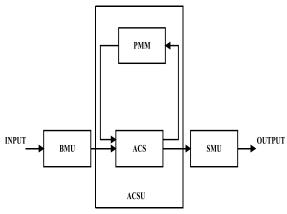

Viterbi Algorithm.

Figure 2: k=1, n=2 and r=1/2 Convolutional Encoder.

Figure 3: Viterbi Decoder Block Diagram.

| DATA INPUT                              | 1000                         | 1011                         | 0001                         | 1100                         |

|-----------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|

| INPUT TO<br>THE<br>ENCODER              | 00 <u>1000</u> 00            | 00 <u>1011</u> 00            | 00 <u>0001</u> 00            | 00 <u>1100</u> 00            |

| OUTPUT OF<br>THE                        | C1: 101000                   | C1: 100111                   | C1: 000101                   | C1: 111100                   |

| ENCODER                                 | C2: 111000                   | C2: 110001                   | C2: 000111                   | C2: 100100                   |

| CODEWORD<br>GENERATED                   | 110110000000                 | 110100101010                 | 000000110111                 | 111010110000                 |

| CODEWORD<br>STORED ON<br>FAULTY<br>SRAM | 110 <u>0</u> 10000000        | 1 <u>0</u> 0100101010        | 000000 <u>0</u> 10111        | 1110101 <u>0</u> 0000        |

| INPUT TO<br>THE                         | C1: 1010000                  | C1: 100111                   | C1: 000 <u>0</u> 01          | C1: 111100                   |

| DECODER                                 | C2: 1 <u>0</u> 00000         | C2: 100001                   | C2: 000111                   | C2: 100 <u>0</u> 00          |

| OUTPUT OF<br>THE<br>DECODER             | 00 <u>1000</u> 00            | 00 <u>1011</u> 00            | 00 <u>0001</u> 00            | 00 <u>1100</u> 00            |

| CODEWORD<br>OF THE<br>RETRIEVED<br>DATA | 110110000000                 | 110100101010                 | 000000110111                 | 111010110000                 |

| XORING<br>CODEWORD                      | 110110000000                 | 110100101010                 | 000000110111                 | 111010110000                 |

| OF SRAM<br>AND DATA<br>RETRIEVED        | XOR<br>110 <u>0</u> 10000000 | XOR<br>1 <u>0</u> 0100101010 | XOR<br>000000 <u>0</u> 10111 | XOR<br>1110101 <u>0</u> 0000 |

| FAULTY<br>SRAM<br>POSITION              | 000 <u>1</u> 00000000        | 0 <u>1</u> 0000000000        | 000000 <u>1</u> 00000        | 0000000 <u>1</u> 0000        |

Figure 4: Example of Convolution Codes.

# V. CYCLIC REDUNDANCY CHECK - CRC

CRC - Cyclic Redundancy Check is a technique for detecting errors in digital information transmission, however not for error correction after errors are recognized. In the CRC strategy, some number of check bits is added. These check bits are called checksum. They are connected to the information bits that are being stored. The beneficiary figures out whether the check bits concur with the information bits. On the off chance that an error

| Dataword | Codeword              | Dataword | Codeword               |

|----------|-----------------------|----------|------------------------|

| 0000     | 000000                | 1000     | 1000101                |

| 0001     | 0001011               | 1001     | 1001110                |

| 0010     | 0010110               | 1010     | 1010011                |

| 0011     | 0011101               | 1011     | 1011000                |

| 0100     | 0100111               | 1100     | 1100010                |

| 0101     | 0101100               | 1101     | 1101 <mark>0</mark> 01 |

| 0110     | 0110 <mark>001</mark> | 1110     | 1110100                |

| 0111     | 0111010               | 1111     | 1111111                |

Figure 5: Example of Generated code words using CRC.

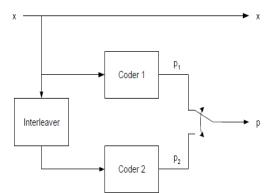

## VI. TURBO CODES

In 1993 Berrou, Glavieux and Thitimajshima proposed "another class of convolution codes called as turbo codes". It a class of Forward Error Correction Codes widely used in communication system.

A turbo code is a parallel concatenation of many RSC codes. The encoder consists of two identical RCS -Recursive Systematic Encoder in parallel. The output of encoder1 and encoder2 are got from the same massage bits. The output code rate of both the encoders is at a rate R=1/3 code.

Figure 6: Turbo Encoder Block Diagram.

| DATAINPUT          | 1110       |

|--------------------|------------|

| ENCODER 1 INPUT    | 01110      |

| ENCODER 1 OUTPUT   | 0011101100 |

| INTERLEAVERINPUT   | 1110       |

| INTERLEAVER OUTPUT | 0111       |

| ENCODER 2 INPUT    | 00111      |

| ENCODER 2 OUTPUT   | 0000111011 |

Figure 7: Turbo Encoder example

main decoder combination of convolutional encoder is has happened then fault location in the memory is detected and replaced with the fault free memory.

# IJARCCE

# International Journal of Advanced Research in Computer and Communication Engineering

**ISO 3297:2007 Certified** Vol. 5, Issue 7, July 2016

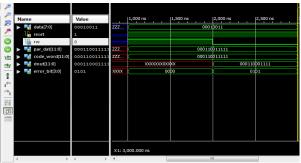

## **VII. SIMULATION RESULTS**

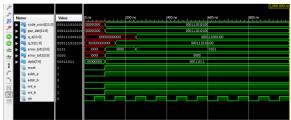

Figure 8: Hamming codes implemented for SRAM.

Figure 9: Hamming codes implemented for Dual Port Memory.

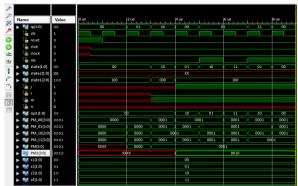

Figure 10: Convolutional Encoder generated code words.

Figure 11: Viterbi Decoder output.

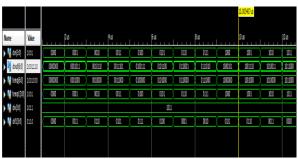

Figure 12: Generated code words using CRC.

Figure 13: CRC code words stored on Memory with error.

| Bus/Signal  | Value |

|-------------|-------|

| SyncIn[0]   | 0     |

| SyncIn[1]   | 1     |

| SyncIn[2]   | 1     |

| SyncIn[3]   | 0     |

| SyncOut[0]  | 0     |

| SyncOut[1]  | 0     |

| SyncOut [2] | 1     |

| SyncOut[3]  | 0     |

| SyncOut[4]  | 1     |

|             |       |

Figure14: Output of CRC using Chipscope Pro

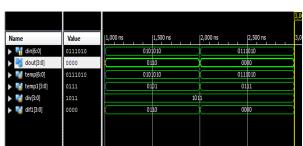

Figure 15: Turbo Encoder output.

#### VIII. COMPARISON OF ERROR CORRECTION CODES TECHNIQUES

| Logic Utilization         | SRAM    | DUAL PORT<br>MEMORY |

|---------------------------|---------|---------------------|

| No. of Slice Latches      | 8(1%)   | 15(1%)              |

| No. of occupied Slices    | 13(1%)  | 18(1%)              |

| Total no. of 4 input LUTs | 25(1%)  | 21(1%)              |

| Maximum path delay        | 8.348ns | 6.530ns             |

| Total On-Chip Power       | 69.18mW | 60.66mW             |

Figure 16: Hamming Codes comparison with SRAM and Dual Port Memory.

| Logic Utilization         | SRAM     | DUAL PORT MEMORY |

|---------------------------|----------|------------------|

| No. of Slice Latches      | 8(1%)    | 368(5%)          |

| No. of occupied Slices    | 8(1%)    | 336(9%)          |

| Total no. of 4 input LUTs | 14(1%)   | 325(4%)          |

| Maximum path delay        | 10.991ns | 10.290ns         |

| Total On-Chip Power       | 59.79mW  | 60.00mW          |

Figure 17: CRC comparison with SRAM and Dual Port Memory

# IJARCCE

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 7, July 2016

| Logic Utilization         | CRC SRAM | HAMMING SRAM |

|---------------------------|----------|--------------|

| No. of Slice Latches      | 8(1%)    | 8(1%)        |

| No. of occupied Slices    | 8(1%)    | 13(1%)       |

| Total no. of 4 input LUTs | 14(1%)   | 25(1%)       |

| Maximum path delay        | 10.991ns | 8.348ns      |

| Total On-Chip Power       | 59.79mW  | 69.18mW      |

Figure 18: Comparison of SRAM of CRC and SRAM of Hamming Codes

| Logic Utilization         | HAMMING DUAL<br>PORT MEMORY | CRC DUAL PORT<br>MEMORY |

|---------------------------|-----------------------------|-------------------------|

| No. of Slice Latches      | 15(1%)                      | 368(5%)                 |

| No. of occupied Slices    | 18(1%)                      | 336(9%)                 |

| Total no. of 4 input LUTs | 21(1%)                      | 325(4%)                 |

| Maximum path delay        | 6.530ns                     | 10.290ns                |

| Total On-Chip Power       | 60.66mW                     | 60.00mW                 |

Figure 19: Comparison of CRC codes and Hamming codes using Dual Port Memory

| Logic Utilization         | CONVOLUTIONAL<br>ENCODER | VITERBI<br>DECODER |

|---------------------------|--------------------------|--------------------|

| No. of Slices             | 7 out of 3584            | 89 out of 3584     |

| No. of occupied Slices    | 6(1%)                    | 92(2%)             |

| Total no. of 4 input LUTs | 12(1%)                   | 171(2%)            |

| Maximum path delay        | 8.094ns                  | 21.370ns           |

| Total On-Chip Power       | 60.60mW                  | 60.55mW            |

Figure 20: Comparison of Convolutional Encoder and Viterbi Decoder.

| Logic Utilization         | TURBO ENCODER     |

|---------------------------|-------------------|

| No. of Slice Flip Flops   | 2 out of 7168(1%) |

| No. of occupied Slices    | 2(1%)             |

| Total no. of 4 input LUTs | 2(1%)             |

| Time from CPU to Xst      | 25.49ns           |

| Total On-Chip Power       | 60.00mW           |

Figure 21: Design Summary of Turbo Encoder.

## IX. CONCLUSION

The aim of this work is to mainly concentrate on Error Correction Coding techniques like Hamming codes, Convolution codes, Cyclic Redundancy Check and turbo codes. These codes are designed with Verilog language and simulated on SPARTAN-3 using XILINX ISE 14.2 and Chipscope Pro.

Though it is very difficult to tell which the best technique is, it is better to run different techniques in parallel and take up the reliability and quality of different techniques to get best throughput.

#### REFERENCES

- Rubal Chaudhary, Vrinda Gupta, "Error Control Techniques and Their Applications", International Journal of Computer Applications in Engineering Sciences.

- [2] Prof. Siddeeq Y. Ameen, Mohammed H. Al-Jammas and Ahmed S. Alenezi, "FPGA Implementation of Modified Architecture for Adaptive Viterbi Decoder" IEEE,2011.

- [3] Wael. M. El-Medany, "FPGA Implementation of CRC with Error Correction", ICWMC 2012, The Eighth International Conference on Wireless and Mobile Communications.

- [4] Miss.Rupinder Kaur, Mr.Shakti Raj Chopra. "Iterative Decoding of Turbo Codes", International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013.

- [5] Eltayeb S. Abuelyaman and Abdul-Aziz S. Al-Schibani, "Optimization of the Hamming Code for Error Prone Media", IJCSNS International Journal of Computer Science and Network Security, VOL.8 No.3, March 2008.